# A Survey on Heuristic Algorithms on Detailed Routing in Physical Design Automation

#### Upasana Yadav<sup>1</sup>, Pragya Sharma<sup>2</sup>, Neeraj Kr. Shukla<sup>3</sup>

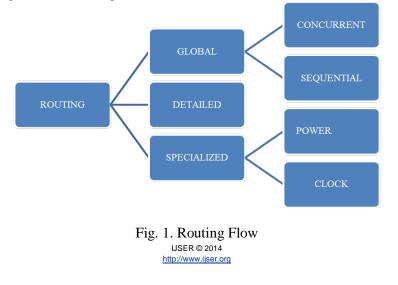

Abstract— Routing is one of the most complex stage in physical design. Detailed routing determines the exact place of tracks and via. The main objective ofdetailed routing is to reduce the area of an integrated chip. Minimization of wire length, number of tracks, channel length, congestion factor is the key problem in physical design. Routing is a process to interconnect all the nets within the channel considering all constraints(horizontal and vertical constraints) of that channel. Unlike traditional routing schemes ,all the traffic is along a single path, multipath routing scheme splitthe traffic among several paths in order to reduce the congestion. In this paper, we analyze different single-layer algorithms, two-layer algorithms and three layer algorithms and conclude that the objective of the routing problems like crosstalk, wire length, channel length, no of tracks and vias.

Index Terms— Algorithm, Detailed routing, Physical design, VLSI CAD

### I. Introduction

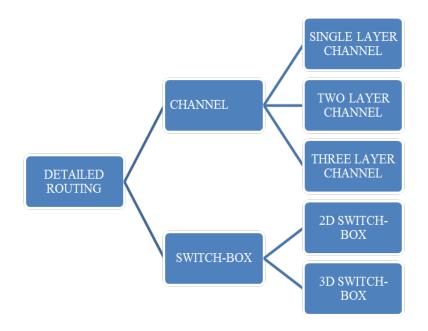

The most important step in the physical design of VLSI circuits is detailed routing. Detailed routing determines the exact tracks and via for nets. The two most popular types of detailed routing: channel routing and full-chip routing. In earlier process technologies when the maximum number of available metal layers was only two or three, channel routing was pervasively used, because most wires were routed in the free space(i.e. routing channel) between a pair of logic blocks. In modern technologies, a chip typically contains six to ten metal layers, and the number of available metal layers is expected to increase steadily in the near future. With more metal layers, routing over the logic block is common. As a result, routing regions become more like channel-less regions. This trend drives the need of a full-chip routing.

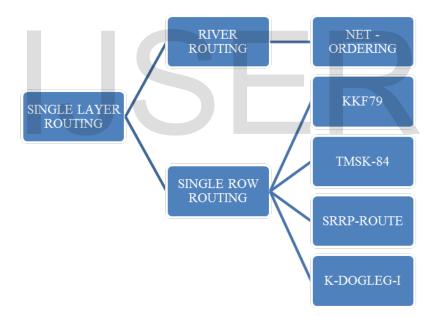

Channel routing plays a important role in a physical design of VLSI chips. Many algorithms have been proposed in the past few years, for single-layer routing [15] and two-layer routing and three-layer routing. Recent studies shows that the network would be more efficient and robust if routers could flexibly divide traffic over multiple paths. Distributed multipath routing algorithm solve the question of path selection and minimize congestion[20]. Crosstalk minimization is done by bubble sorting based manhatten channel router and rerouting algorithm in four-layer non-manhattan channel routing[28].

The remainder of the paper is organized as follow: section II describes the evolution tree of detailed routing and algorithms in detailed routing. In Section III, we present our survey work. Finally, we conclude our work in section IV.

## **II. Detailed Routing - The Evolution Tree**

Detailed routing problem is solved by solving one routing region at a time. The routing area is first partitioned into smaller regions. Since, the global router only assign wires to different regions, the detailed routing problem is to find the actual geometric path for each wire in a region. Shape of the region is the most important factor.

Fig. 1a. Detailed Routing

Fig. 1b. Single Layer Routing

# **Detailed Routing Algorithms**

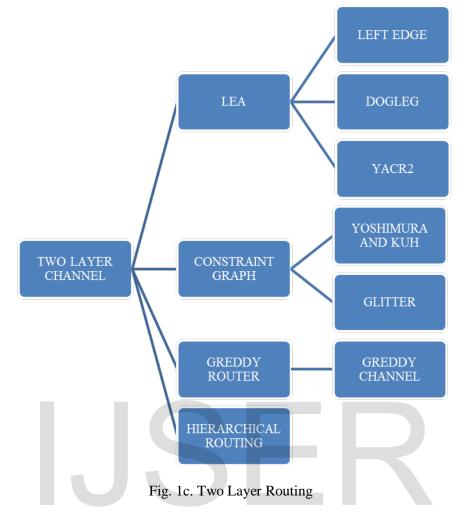

| .LEA       | The algorithm was designed to route array-based two layer PCBs. It uses a reserved layer modelit doesnot allow doglegs and any vertical constraints.                                                                    |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ii.DOGLEG  | Drawback of LEA is overcome by this algorithm. The dogleg router isthatit allows multiterminal netsand vertical constraints.                                                                                            |

| iii.YACR2  | This algorithm explain how vertical constraints violation are handled and define the concept of vertical overlap fac tor, which indicate the total number of tracks that a vertical constraint violation spans.         |

| iv. Y-K    | It is based on net merging. It include both horizontal and vertical constraints graphs and assign tasks to nets so as to minimize the effect of vertical constraint chain in the vertical constraint                    |

| v. GLITTER | A grid-less variable-width channel router called glitter. Glitter can utilize multiple layer technology.                                                                                                                |

| vi. GREEDY | The algorithm start from the left most column and place all the nets and segments of a column beforeproceedings to the next right column. In each column, the router assigns net segments to tracks in a greedy manner. |

# **III.** Literature Survey

| QNE HILL NOHLOE<br>"A New<br>algorithms<br>with Mini-<br>mum<br>Tracks for<br>Four Layer<br>Channel<br>Routing in<br>VLSI De-<br>sign"Ajoy<br>Kumar<br>Khan ,<br>Bhaskar<br>Das [1]                                                  | CONFERENCE<br>CONFERENCE                                           | ADD EDA<br>ADD EDA<br>ADD EDA<br>AND EDA<br>AND EDA<br>ADD EDA<br>ADD EDA | Vertical Con-<br>straint<br>Graph(VCG),<br>Horizontal<br>Constraint<br>Graph(HCG)<br>Horizontal non<br>Constraint<br>Graph(HNCG) | H H H H H H H H H H H H H H H H H H H                 | SLUENHUP<br>Reduced<br>the no. of<br>tracks<br>needed for<br>channel<br>routing<br>problem<br>then au-<br>tomatical-<br>ly the area<br>of an IC<br>chip is<br>also re-<br>duced | SNOLLY LIWIT There is no close loop in the VCG of that channel that means the VCG must be tree | HOOS<br>HADDE<br>If there is<br>a cycle in<br>VCG.<br>a) Add a<br>vertical<br>layer. Then<br>it becomes<br>a five layer<br>channel<br>problem.<br>So we draw<br>some algo-<br>rithms for<br>this pur-<br>pose. | a) Know about<br>transitively orient-<br>ed graph.<br>b) reduction the no<br>of tracks gives<br>good result                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "Yet an<br>Efficient<br>Algorithm<br>for Compu-<br>ting Re-<br>duced Area<br>VLSI<br>Channel<br>Routing<br>Solution<br>With Float-<br>ing Termi-<br>nals<br>"Achire<br>Pal, Swaga-<br>taSahaSau,<br>Ta-<br>rakN.Mand<br>al et-al.[2] | 2011<br>IEEE<br>Proceed-<br>ings of<br>14 <sup>th</sup> IC-<br>CIT | C pro-<br>gram-<br>ming<br>lan-<br>guage                                  | Vertical con-<br>straint<br>graph(VCG),<br>Horizontal non<br>constraint<br>graph(HNCG)                                           | Density of the<br>channel = no. of<br>tracks required | Reduction<br>of area or<br>the chan-<br>nel width                                                                                                                               |                                                                                                | The algo-<br>rithms for<br>completing<br>routing<br>solutions<br>with re-<br>duced wire<br>length and<br>doglegging                                                                                            | <ul> <li>a) NP problem is<br/>solved by pro-<br/>posed algorithm.</li> <li>b)reduction chan-<br/>nel area under the<br/>reserved two-layer<br/>Manhattan no-<br/>dogleg channel.</li> </ul> |

| "A Graph<br>Theoretic<br>Approach<br>to Mini-<br>mize Total<br>Wire<br>Length in<br>Channel<br>Rout-<br>ing"Pralay<br>Mitra et. al<br>[3]                                                    | 2003<br>IEEE                               |                                                          | Using TAH<br>framework,<br>reduction the<br>total wire<br>length.                                     |                                                                                                                                | Minimiza-<br>tion of<br>total wire<br>length for<br>two layer<br>channel<br>routing.                                                                  | Does not<br>use back-<br>tracking                                                                          | a) exten-<br>sion to<br>computer<br>reduced<br>wirelength<br>routing<br>solution in<br>the re-<br>served<br>three-layer<br>HVH and<br>VHV rout-<br>ing models.                 | This algorithm<br>does notuse much<br>area in computing<br>such solution.                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| "An Effi-<br>cient High<br>Perfor-<br>mance Par-<br>allel Algo-<br>rithm to<br>Yield Re-<br>duced Wire<br>Length<br>VLSI Cir-<br>cuits".<br>Swaga-<br>taSahaSau,<br>Rajat Ku-<br>mar Pal [4] | 2012<br>IEEE<br>5 <sup>th</sup> CO-<br>DEC | C++                                                      | High perfor-<br>mance parallel<br>algorithm<br>MTAH is com-<br>putation by<br>small small<br>modules. | For r2: 21.03%<br>Ex5: 27.97%<br>Reduction in<br>total wire length<br>in a solution<br>computed using<br>our algorithm<br>MTAH | Different<br>modules<br>of MTAH<br>run in<br>parallel so<br>it requires<br>less exe-<br>cution<br>time and<br>reduces<br>the total<br>wire<br>length. | Algo-<br>rithm<br>require<br>constant<br>number<br>of pro-<br>cessor<br>(or a<br>single<br>proces-<br>sor) | Computing<br>reduced<br>wire length<br>routing<br>solution in<br>the re-<br>served<br>three and<br>multi-layer<br>no-dogleg<br>as well as<br>and dogleg<br>routing<br>modules. | <ul><li>a) In which compu-<br/>tation time is neg-<br/>ligibly small</li><li>b) MTAH requires<br/>one ,two or three<br/>tracks.</li></ul> |

| "A Firefly<br>Algorithm<br>Approach<br>for Routing<br>in VLSI"<br>M.NasirAy<br>ob, Fariz<br>Hassan,et-<br>al. [5]                                                                            | 2012<br>IEEE IS-<br>CAIE                   | Visual<br>basic 6,<br>Use size<br>of<br>22* 17<br>grids. | Delay model<br>Elmore delay<br>Calculation and<br>grid-graph<br>model                                 | The optimal so-<br>lution of the case<br>study which is<br>571.73ps                                                            | Find min-<br>imum<br>time delay<br>by choos-<br>ing the<br>path and<br>placing<br>the buffer<br>intelli-<br>gently                                    | -                                                                                                          | Using other<br>optimiza-<br>tion tech-<br>niques such<br>as magnetic<br>optimiza-<br>tion algo-<br>rithm and<br>paddy field<br>algorithm.                                      | Examine the fit-<br>ness of new firefly<br>and updating the<br>light intensity.                                                           |

| "A Routing<br>Framework<br>for Delay<br>Tolerant<br>Networks<br>Based on<br>Encounter<br>Angle "Yue<br>Cao,<br>Haitham<br>Cruick-                             | 2011<br>IEEE                                                                         | C++<br>lan-<br>guage                                                                               | <ul><li>a) Calculation<br/>of the encoun-<br/>ter angle.</li><li>b) Probabilistic<br/>replication</li><li>c) Routing<br/>framework</li></ul> |                                                                                                             | Reduces<br>the num-<br>ber of<br>aborted<br>messages<br>due to<br>mobility<br>factor and<br>achieves<br>the signif-<br>icant per- |                                                                                                                                                | <ul> <li>a) More intelligent mechanism for the routing framework</li> <li>b) optimize the estimation of po-</li> </ul> | a) battery con-<br>sumption function<br>is also integrated<br>into algorithms b)<br>reduce the no. of<br>transmissions for<br>efficient bandwidth<br>usages.                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| shank, Zhili<br>Sun. [6]                                                                                                                                      |                                                                                      |                                                                                                    |                                                                                                                                              |                                                                                                             | formance                                                                                                                          |                                                                                                                                                | tential en-<br>counter<br>duration<br>with low<br>complexity.                                                          |                                                                                                                                                                                                                                                              |

| "Encounter-<br>Based<br>Routing in<br>Delay Tol-<br>erant Net-<br>works"<br>Jun-<br>baozhang,G<br>uangchun-<br>lua, Ke Qin<br>Haifeng<br>Sun. [7]             | 2011<br>IEEE                                                                         | Oppor-<br>tunistic<br>network<br>envi-<br>ronment<br>(ONE)<br>simula-<br>tor ver-<br>sion<br>1.4.0 | Simulation set-<br>up<br>Effect of trans-<br>mission range<br>Effect of stor-<br>age capacity                                                | <b>BE</b>                                                                                                   | EBR has<br>good per-<br>formance<br>and low<br>overhead<br>in sparse<br>network.                                                  |                                                                                                                                                | Analysis to<br>real mobili-<br>ty traces<br>and hetero-<br>geneous<br>networks.                                        | EBR exploits inter-<br>contact time to<br>predict the no of<br>contacts from now<br>to the expected<br>delay.                                                                                                                                                |

| "GDRouter:<br>Interleaved<br>Global<br>Routing<br>and De-<br>tailed Rout-<br>ing for Ul-<br>timate<br>Routabil-<br>ity"Yanhen<br>g Zhang<br>Chris Chu.<br>[8] | 2012<br>DAC                                                                          | C lan-<br>guage                                                                                    | GDRouter<br>a)Fast<br>route(global)<br>b)Regular<br>route(detailed)                                                                          | Reduce number<br>of unassigned<br>global segment<br>by :<br>a) 90% for<br>ISPD98<br>b) 60% for<br>ISPD05/06 | Enhanced<br>routability                                                                                                           | GDRout-<br>er quits<br>the loop<br>if de-<br>tailed<br>routing<br>routabil-<br>ity stops<br>improv-<br>ing or<br>reaches<br>max.<br>iteration. | The solu-<br>tion quality<br>of the inter-<br>leaved<br>global rout-<br>ing and<br>detailed<br>routing<br>algorithms.  | <ul> <li>a) spine routing<br/>and virtual routing<br/>are applied to gen-<br/>erate initial global<br/>capacity.</li> <li>b) GDRouter: an<br/>interleaved global<br/>and detailed rout-<br/>ing algorithm for<br/>the ultimate routa-<br/>bility.</li> </ul> |

| "A Novel<br>Detailed<br>Routing<br>Algorithm<br>with Exact<br>Matching<br>Constraint<br>for Analog                                                            | 2011<br>IEEE<br>12 <sup>th</sup> Int'l<br>Symposi-<br>um on<br>Quality<br>Electronic | C++<br>lan-<br>guage<br>run on<br>Linux<br>server<br>with<br>Intel(R)                              | Detailed rout-<br>ing:<br>a) Grid algo-<br>rithm<br>b) Gridless<br>algorithm                                                                 | 10X speedup                                                                                                 | Size of the<br>routing<br>area with<br>the exact<br>matching<br>con-<br>straints is<br>often                                      |                                                                                                                                                | Algorithm<br>to consider<br>shielding<br>and other<br>geometric<br>constraints.                                        | Investigation of<br>bounded-error<br>matching routing<br>beyond the exact<br>matching routing.                                                                                                                                                               |

| and Mixed<br>Signal Cir-<br>cuits"Qiang<br>Gao,Hailon<br>g Yao Qi-<br>ang-<br>Zhou,YciC<br>ai. [9]                                                                                              | Design                                                                                                      | Xeon(T<br>M)300<br>GHZ<br>CPU            |                                                                                                                                                    |                                                                          | small<br>enough to<br>directly<br>apply de-<br>tailed<br>routing                                                                                       |                                                                                                                                          |                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "Dangling-<br>wire<br>Avoidance<br>Routing for<br>Crossbar<br>Switch<br>Structured<br>ASIC De-<br>sign<br>Style"Yi-<br>Huang<br>Hung<br>Hung-Yi Li<br>, Po- Yang<br>Hsu ,Yi-<br>Yu-Liu.<br>[10] | 2010<br>IEEE<br>Work is<br>supported<br>in<br>National<br>Science<br>Council of<br>Taiwan                   |                                          | Steiner three<br>construction:<br>a)Pin assign-<br>ment<br>b) Dangling<br>wire aware<br>c) Anchor pair<br>insertion for<br>congestion re-<br>moval | 21% dangling<br>wire<br>34% channel<br>width<br>13% total wire<br>length | Crossbar<br>switch<br>routing<br>frame-<br>work re-<br>duces:<br>a) dan-<br>gling-wire<br>b) total<br>wire<br>length<br>c) routing<br>conges-<br>tion. |                                                                                                                                          | <br>Proposed a) a high<br>speed crossbar<br>switch routing<br>framework<br>b) graph model for<br>crossbar switch<br>routing.                                   |

| "Graph<br>Colouring<br>Based Mul-<br>ti Pin Net<br>Detailed<br>Routing for<br>FPGA us-<br>ing SAT"<br>Shyamapa-<br>da Mukher-<br>jee, Suchi-<br>smita Roy<br>[11]                               | 2013<br>IEEE<br>3 <sup>rd</sup> IACC                                                                        | C pro-<br>gram-<br>lan-<br>guage         | Modeled the<br>FPGA as a col-<br>ourablegraph.<br>Demonstrated<br>SAT-based<br>FPGA detailed<br>routing                                            | Minimization of<br>channel width                                         |                                                                                                                                                        | Consider<br>all multi-<br>pin nets<br>simulta-<br>neously                                                                                | <br>Net ordering is a<br>big issue in the net<br>at a time approach<br>because invalid<br>sequence of net-<br>selection may<br>cause the algorithm<br>to fail. |

| "The Au-<br>tomation<br>design<br>Based on<br>Graphs for<br>the Sym-<br>metrical<br>Routing in<br>Integrated<br>Circuit"<br>Xu-                                                                 | 2011<br>IEEE<br>2011 In-<br>ternational<br>Confer-<br>ence on<br>System<br>Science,<br>Engineer-<br>ing De- | C pro-<br>gram-<br>ming<br>lan-<br>guage | <ul><li>a) Theorems</li><li>b) Algorithms</li><li>c) Corollary</li><li>d) Conjecture</li></ul>                                                     |                                                                          | A new<br>heuristic<br>algorithm<br>based on<br>the con-<br>clusion to<br>solve the<br>problem<br>of 2-layer<br>manhattan                               | <ul> <li>a) Verti-<br/>cal con-<br/>straints<br/>are<br/>noncy-<br/>clic</li> <li>b) extra<br/>empty<br/>columns<br/>and dog-</li> </ul> | <br>The minimum<br>parallel clique cov-<br>er of CCG is equal<br>to the optimal solu-<br>tion of 2-layer<br>manhattan channel<br>routing.                      |

| Zhenghua.<br>[12]                                                                                                                                          | sign and<br>Manufac-<br>turing<br>Informati-<br>zation |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                               | channel<br>routing                                                                                  | legs are<br>not al-<br>lowed                                                                  |                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| "Crossing-<br>Aware<br>Channel<br>Routing<br>For Photon-<br>ic Wave-<br>guides"<br>Christopher<br>Condrat,<br>Priyank-<br>Kalla, Ste-<br>ve Blair.<br>[13] | 2013<br>IEEE                                           | <br>                                                                                                                                                                                                         | <ul> <li>a) CA(crossing-<br/>aware)reduces</li> <li>the no of cross-<br/>ing to 0.607 ×</li> <li>produce by</li> <li>YK(Yoshimura-<br/>Kuh)router</li> <li>b) cost of rough-<br/>ly 1.25×no of<br/>tracks.</li> </ul>                                                         |                                                                                                     | Cross-<br>ing-<br>minimi-<br>zation-<br>comes at<br>the cost<br>of addi-<br>tional<br>tracks. | <br><ul><li>a) It uses left edge-<br/>style channel rout-<br/>ers.</li><li>b) signal losses is<br/>reduced by channel<br/>router.</li></ul> |

| "Analytical<br>Placement<br>of Mixed-<br>size Cir-<br>cuits for<br>Better De-<br>tailed-<br>Routabil-<br>ity" Shuai-<br>Li ,Cheng-<br>KokKoh.<br>[14]      | 2014<br>IEEE                                           | Main two Con-<br>tribution are:<br>a) A new ana-<br>lytical place-<br>ment formula-<br>tion with pin<br>density con-<br>straints<br>b)scaled<br>smoothing<br>method to cope<br>with fixed mac-<br>ro blocks. | <ul> <li>a) avgwire-<br/>length&amp; via</li> <li>count are 4%</li> <li>smaller than rip-<br/>ple &amp;simPLR</li> <li>b) compared</li> <li>with NTUplace4</li> <li>- avg wire</li> <li>length:1.9%</li> <li>larger</li> <li>- avg via count</li> <li>1.0% smaller</li> </ul> | Technique<br>are effec-<br>tive in<br>improving<br>the routa-<br>bility of<br>placement<br>results. | Target<br>density<br>t <sub>den</sub> is set<br>to be<br>0.80                                 | <br>Detailed routing<br>solutions with few-<br>er violations can be<br>generated in a<br>shorter time for the<br>proposed place-<br>ment    |

| "Short -                | 2014       |        | a) Short -Term          |                   | High ac-        |                | This ap-                 | Requirement:                           |

|-------------------------|------------|--------|-------------------------|-------------------|-----------------|----------------|--------------------------|----------------------------------------|

| Term Hy-                | IEEE       |        | Hydrothermal            |                   | curacy of       |                | proach to                | -                                      |

| drothermal              | Transac-   |        | Dispatch prob-          |                   | proposed        |                | be used as               | a) hydro plants                        |

| Dispatch                | tions on   |        | lem.                    |                   | approach        |                | a guideline              | h)th anno 1 a lan ta                   |

| With River-             | Power      |        |                         |                   | to repre-       |                | for actual               | b)thermal plants                       |

| Level and               | Systems    |        | b) River Level          |                   | sent max-       |                | system                   | c) high accuracy                       |

| Routing                 |            |        | Constraints.            |                   | imum            |                | operation.               | e) mgn weenreej                        |

| Con-                    |            |        | c) River Rout-          |                   | hourly and      |                |                          |                                        |

| straints."An            |            |        | ing Constraints.        |                   | daily riv-      |                |                          |                                        |

| dre                     |            |        | ing Constraints.        |                   | er-level        |                |                          |                                        |

| LuizDiniz,              |            |        |                         |                   | variations      |                |                          |                                        |

| Thiago                  |            |        |                         |                   | without         |                |                          |                                        |

| Moto Sou-               |            |        |                         |                   | increase in     |                |                          |                                        |

| za. [15]                |            |        |                         |                   | CPU time        |                |                          |                                        |

|                         |            |        |                         |                   |                 |                |                          |                                        |

| "Efficient              | 2014       |        | a)LBDRx is a            | Minimize the      | Reduce          | Reduce         | Further                  | Routing tables                         |

| Routing in              | IEEE       |        | series of routing       | overall cost      | the size of     | logic          | explore the              | were replaced by                       |

| heteroge-               | T          |        | mechanisms              |                   | routing         | cost,          | mapping                  | the LBDRx mech-                        |

| neous SoC               | Transac-   |        | 1.) A                   |                   | tables          | regard-        | tool focus-              | anism.                                 |

| Designs                 | tions on   |        | b) A mapping<br>tool    |                   | either at       | less of        | ing on per-              |                                        |

| with Small              | Comput-    |        | 1001                    |                   | end nodes       | system         | formance                 |                                        |

| Implemen-               | ers        |        |                         |                   | or at rout-     | size           | issues and               |                                        |

| tation over-            |            |        |                         |                   | ers.            |                | to optimize              |                                        |

| head"Jose               |            |        |                         |                   |                 |                | the tool to              |                                        |

| Cano, Jase-             |            |        |                         |                   |                 |                | provide the              |                                        |

| Flich et al. [16]       |            |        |                         |                   |                 |                | best map-                |                                        |

| [10]                    |            |        |                         |                   |                 |                | ping for the target app. |                                        |

|                         |            |        |                         |                   |                 |                | taiget app.              |                                        |

|                         | 2014       |        |                         |                   | <b>D</b> 1 1    |                |                          |                                        |

| "A Boolean              | 2014       |        | IPL(integer             | Wire length re-   | Reduced         | Perfor-        | This EDA                 | The main reduction                     |

| Rule-                   | IEEE       |        | linear pro-             | duction $= 1.6\%$ | logic cost      | mance,         | tool will                | was in horizontal<br>and vertical, but |

| Based Ap-<br>proach for | Transac-   |        | gramming) and LNS(large |                   | regardless      | power,<br>area | enable the exploration   | this reduction was                     |

| Manufac-                | tions on   |        | neighborhood            |                   | of system size. | area           | and charac-              | compensated by an                      |

| turability-             | Comput-    |        | search) algo-           |                   | 5120.           |                | terization               | increase of vertical                   |

| Aware Cell              | er-Aided   |        | rithm for rout-         |                   |                 |                | of wide                  | and increase of                        |

| Rout-                   | Design of  |        | ing optimiza-           |                   |                 |                | range of                 | vias.                                  |

| ing"Jordi               | Integrated |        | tion                    |                   |                 |                | layout tem-              | 1405.                                  |

| Cortadella,             | Circuits   |        | uon                     |                   |                 |                | plates for               |                                        |

| Jordi Petit.            | and Sys-   |        |                         |                   |                 |                | cell librar-             |                                        |

| et al. [17]             | tems       |        |                         |                   |                 |                | ies.                     |                                        |

|                         |            |        |                         |                   |                 |                |                          |                                        |

| "An Effi-               | 2013       | C lan- | Two approach-           | a)15% reduction   | a)Improve       |                | Delay and                | To avoid blockage                      |

| cient inter-            |            | guage  | es:                     | in wirelength     | d intersec-     |                | Crosstalk                | during routing                         |

| section                 |            |        | a)Sequential            | b) reduces CPU    | tion be-        |                | can be re-               | Weight-based stei-                     |

| Avoiding                |            |        |                         | execution time.   | tween nets      |                | duced and                | ner edge technique                     |

| Rectilinear             |            |        | b)Concurrent            |                   | and con-        |                | pin multi                | used.                                  |

| Routing<br>Technique    |            |        |                         |                   | gestion         |                | net routing<br>using non |                                        |

| in VLSI"                |            |        |                         |                   | b)Minimiz       |                | manhattan                |                                        |

| Pratha-                 |            |        |                         |                   | ed block-       |                | mannattall               |                                        |

| 1 Iuulu                 |            |        |                         |                   |                 |                |                          |                                        |

| pratimsaha,<br>suman-<br>tasaha,andt<br>uhinasa-<br>manta[18]                                                                                                                   |                                                                                                        |                                                           |                                                                                                                                                                                                                            |                                                                           | age in<br>routing                                                                                                                 |                                            | routing                                                                                                                                                                       |                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| "Regular<br>Route : An<br>Efficient<br>Detailed<br>Router Ap-<br>plying<br>Regular<br>Routing<br>Pat-<br>terns"Yanh<br>eng Zhang<br>Chris Chu.<br>[19]                          | 2013<br>IEEE<br>Transac-<br>tions On<br>Very<br>Large<br>Scale In-<br>tegration<br>(Vlsi)<br>Systems   |                                                           | <ul> <li>a)Algorithm</li> <li>proceeds in a</li> <li>bottom-up layer</li> <li>-by- layer manner:</li> <li>a) Local net</li> <li>routing</li> <li>b) Global segment</li> <li>assignment</li> <li>c) Optimization</li> </ul> | 20%-30% less<br>metal 2 usage                                             | a)Effectiv<br>eness and<br>Efficiency<br>of Regular<br>Route.<br>b)Minor<br>impact<br>for density<br>control                      | 4 * 4 G-<br>cell to<br>form one<br>region. | <ul> <li>a) Improve<br/>the perfor-<br/>mance of<br/>Regular<br/>Route</li> <li>b) A paral-<br/>lel version<br/>of tool for<br/>further<br/>runtime<br/>reduction.</li> </ul> |                                                                                                                                  |

| "A Distrib-<br>uted Multi-<br>path Rout-<br>ing Algo-<br>rithm To<br>Minimize<br>Conges-<br>tion"<br>GuoXin,<br>Zhang Jun,<br>Zhang Jun,<br>[20]                                | 2009<br>IEEE<br>28th Dig-<br>ital Avi-<br>onics Sys-<br>tems Con-<br>ference                           |                                                           | Distributed<br>Congestion-<br>Minimized<br>Multipath<br>(D-CMM):-<br>a)Congestion<br>facto<br>b)Network<br>throughput<br>c)Delay                                                                                           | Congestion fac-<br>tor < 1.0                                              | a)Increase<br>network<br>through-<br>put<br>b) De-<br>crease<br>conges-<br>tion factor<br>c)Increase<br>of shortest<br>path delay | Transfer<br>delay                          |                                                                                                                                                                               | Proposed algorithm<br>is more suitable in<br>long distance<br>transmission and<br>dense network to-<br>pology.                   |

| "A Fast<br>Placement<br>and Global<br>Routing<br>Integrated<br>Algorithm<br>for Hierar-<br>chical<br>FPGAs"<br>Limin Zhu,<br>Jinan Bi-<br>an,Qiang<br>Zhou<br>,YieiCai.<br>[21] | 2011<br>Interna-<br>tional<br>Confer-<br>ence on<br>Infor-<br>mation<br>Science<br>and Tech-<br>nology | C++<br>pro-<br>grams<br>includ-<br>ing<br>netlist<br>file | For reduction of<br>mismatch in<br>HFPGA :<br>a) New Place-<br>ment<br>b) New Global<br>Routing<br>c) Detailed<br>Routing                                                                                                  | Alu4 : 3.98(<br>CPU/s)<br>Seq : 3.96(<br>CPU/s)<br>Frg1 : .011(<br>CPU/s) | CPU time<br>get larger<br>very slow-<br>ly as the<br>circuit<br>become<br>larger.                                                 |                                            |                                                                                                                                                                               | A placement and<br>global routing al-<br>gorithm is present-<br>ed to solve the<br>mismatch problems<br>between the two<br>FPGA. |

| "A Fast<br>Recursive<br>Detailed<br>Routing<br>Algorithm<br>for Hierar-<br>chical<br>FPGAs"<br>Limin Zhu,<br>Jinan Bi-<br>an,Qiang<br>Zhou<br>,YieiCai.<br>[22]                      | 2011<br>15th In-<br>ternational<br>Confer-<br>ence on<br>Computer<br>supported<br>Coopera-<br>tive Work<br>in Design | C++<br>pro-<br>grams<br>includ-<br>ing<br>netlist<br>file                               | Algorithm for<br>hierarchical<br>FPGAs (HFP-<br>GAs):<br>a)Architecture<br>b)Switchbox<br>Connection<br>Patterns<br>c)Validity of<br>Recursive Rout-<br>ing                 | Alu4 : 1 Rep<br>Seq : 2 Rep<br>Frg1 : 0 Rep<br>* Rep: count of<br>repetitions                                                                                                                   | CPU time<br>get larger<br>very slow-<br>ly due to<br>its recur-<br>sive na-<br>ture |                                                                                             |                                                                                         | A recursive de-<br>tailed routing is<br>presented to specif-<br>ically solve the<br>routing problems<br>for hierarchical<br>FPGA                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "A Two-<br>Step Heu-<br>ristic Algo-<br>rithm for<br>Minimum-<br>Crosstalk<br>Routing<br>Resource<br>Assign-<br>ment"<br>Yicicai,Bin<br>Liu,Qiang<br>Zhou,<br>Xianlong<br>Hong. [23] | 2006<br>IEEE<br>Transac-<br>tions on<br>Circuits<br>and Sys-<br>tems—II                                              | C++                                                                                     | Two stage algo-<br>rithm for cross-<br>talk minimiza-<br>tion in an inte-<br>grated routing<br>resource as-<br>signment stage<br>between global<br>& detailed rout-<br>ing. | BE                                                                                                                                                                                              | Reduce<br>the cross-<br>talk.                                                       | Reduce<br>crosstalk<br>as well<br>as in-<br>crease<br>the com-<br>pleting<br>rate.          | Wire siz-<br>ing/spacing<br>introduce<br>into our<br>framework.                         | Two criteria are<br>used to measure the<br>crosstalk across the<br>chip :<br>a) no of segments<br>that are sensitive to<br>each other and<br>placed adjacently<br>b) no. of failed<br>segments |

| "Double<br>Patterning-<br>Aware De-<br>tailed rout-<br>ing with<br>Mask Us-<br>age Balanc-<br>ing" Seong-<br>I Lei,Chris<br>Chu, Wai-<br>Kei Mak.<br>[24]                            | 2014<br>IEEE                                                                                                         | C++<br>Pro-<br>gram-<br>ming<br>Lan-<br>guage<br>32nm<br>and<br>22nm<br>tech-<br>nology | -Double pat-<br>terning lithog-<br>raphy(DPL)<br>-Maze Routing<br>with Stitch<br>Minimization<br>-Negotiated<br>Congestion<br>based rip-up<br>and reroute                   | For non- pre-<br>ferred routing:<br>->1.9% : shorter<br>wirelength<br>->85.2% less<br>stitches<br>-> 18.8% more<br>vias<br>->98.2% less<br>coloring con-<br>flicts<br>For preferred<br>routing: | a)Faster<br>b)Improve<br>ment on<br>the num-<br>ber of<br>stitches                  | Stitch_co<br>st =30<br>Via_cost<br>=10<br>$\alpha$ = 0.49<br>Targeted<br>range<br>0.49-0.51 | TPL or<br>multiple<br>patterning<br>lithography<br>in detailed<br>routing<br>algorithm. | First fix the color<br>of each track in the<br>routing grid and<br>perform detailed<br>routing using these<br>pre-colored tracks.                                                              |

|                                                                                                                                                       |                                                                                                    |                                                      |                                                                                                                                                | ->0.2% : shorter                                                                                                                                                                  |                                                                                                                                 |                                                                                                                                                                |                                                             |                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                       |                                                                                                    |                                                      |                                                                                                                                                | wirelength                                                                                                                                                                        |                                                                                                                                 |                                                                                                                                                                |                                                             |                                                                                                                                |

| "DFM<br>Based De-<br>tailed Rout-<br>ing Algo-<br>rithm for<br>ECP and<br>CMP" Yin<br>Shen,<br>YiciCai,<br>Qiang<br>Zhou,<br>Xianlong-<br>Hong . [25] | 2008<br>IEEE<br>9th Inter-<br>national<br>Symposi-<br>um on<br>Quality<br>Electron-<br>ics Design  |                                                      | CMR algorithm<br>has main two<br>steps:<br>a) maze search-<br>ing step<br>b) maze back-<br>tracking step.                                      | ->9% less vias<br>CMR vs MR<br>14.6% metal<br>density<br>0.96% avg<br>amount of dum-<br>my fill<br>CMR vs DMR<br>6.99% metal<br>density<br>0.72% avg<br>amount of dum-<br>my fill | a) increase<br>total wire-<br>length<br>b) total<br>number of<br>vias                                                           | Minimiz-<br>ing the<br>metal<br>density<br>and the<br>amount<br>of dum-<br>my fill<br>metal<br>while the<br>wire<br>length<br>and vias<br>are not<br>increased | More accurate ECP and CMP model into the routing algorithm. | <ul> <li>a)</li> <li>Consider metal density .</li> <li>b) flatness of chips and improve the yield of semiconductor.</li> </ul> |

| "Detailed-<br>Routing<br>Algorithms<br>for Dense<br>Pin Clus-<br>ters in Inte-<br>grated Cir-<br>cuits" Mu-<br>hammet<br>Mustafa                      | 2009<br>IEEE<br>Transac-<br>tions on<br>Comput-<br>er-Aided<br>Design of<br>Integrated<br>Circuits | C++<br>GNU<br>Linear<br>Pro-<br>gram-<br>ming<br>Kit | <ul> <li>a) A polynomi-<br/>al-time optimal<br/>algorithm</li> <li>b) An MCF-<br/>based model</li> <li>c) An LR-based<br/>algorithm</li> </ul> | <ul> <li>78% reduces the number of final opens</li> <li>Avg via counts per net by 4%</li> <li>34% decrease the total execution times</li> </ul>                                   | <ul> <li>a) reduce</li> <li>the number of nets</li> <li>b) CPU-time requirements</li> <li>increase</li> <li>with in-</li> </ul> |                                                                                                                                                                |                                                             |                                                                                                                                |

| Ozdal. [26]                                                                                                                                           | and Sys-<br>tems                                                                                   |                                                      |                                                                                                                                                |                                                                                                                                                                                   | creasing<br>cluster<br>size                                                                                                     |                                                                                                                                                                |                                                             |                                                                                                                                |

| "An Inte-<br>ger-Linear-<br>Program-<br>ming-Based<br>Routing<br>Algorithm<br>for Flip-<br>Chip De-<br>signs" Jia-<br>Wei Fang,<br>Chin-<br>Hsiung<br>Hsu, Yao-<br>Wen<br>Chang. [27] | 2009<br>IEEE<br>Transac-<br>tions on<br>Comput-<br>er-Aided<br>Design of<br>Integrated<br>Circuits<br>and Sys-<br>tems | C++<br>program<br>gram-<br>ming<br>lan-<br>guage | Three reduction<br>technique on<br>the problem<br>size:<br>a) Constraint-<br>graph-based<br>pruning<br>b) ILP node<br>merging<br>c) ILP edge<br>bounding                          | ILP node merg-<br>ing:<br>Reduce the vari-<br>ables (con-<br>straints) by avg<br>84.0%(97.9%)<br>ILP edge bound-<br>ing:<br>Reduce the vari-<br>ables (con-<br>straints) by<br>avg7.0%(9.5%) | RDL rout-<br>er for the<br>flip-<br>chip(FC)<br>package<br>minimiza-<br>tion are:<br>a) signal<br>skews<br>b) wire<br>widths<br>c) total<br>wirelength |   |                                                                                                                   |                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "Crosstalk<br>Minimiza-<br>tion in<br>Four-Layer<br>Non-<br>Manhattan<br>Channel<br>Routing"<br>Yongbin<br>Yu, Bo<br>Yang,<br>Yuliang-<br>Zhang,Jueb<br>ang Yu.<br>[28]               | 2004<br>IEEE                                                                                                           | C++                                              | Two algorithms<br>are followed :<br>a) An improved<br>bubble sorting<br>based non-<br>manhattan<br>channel router<br>b) A rerouting<br>algorithms                                 | reduce the cross-<br>talk by an aver-<br>age of 27.9%                                                                                                                                        | Minimiza-<br>tion of<br>crosstalk                                                                                                                      | R |                                                                                                                   | Solve the gridded<br>non-Manhattan<br>channel routing<br>problem with the<br>consideration of<br>crosstalk by modi-<br>fying the existing<br>bubble-sorting al-<br>gorithm |

| "Algo-<br>rithms for<br>High per-<br>formance<br>Two-Layer<br>Channel<br>Routing"<br>Achira<br>Pal,Debojit<br>Kundu, et<br>al. [29]                                                   | 2007<br>IEEE                                                                                                           |                                                  | Algorithms for<br>crosstalk mini-<br>mization:<br>a) Track-<br>interchange(for<br>simple channel<br>instances)<br>b) Track inter-<br>change(for sim-<br>ple channel<br>instances) | 30.77% reduced<br>crosstalk                                                                                                                                                                  | Reduction<br>of cross-<br>talk                                                                                                                         |   | Algorithm<br>for reduc-<br>ing cross-<br>talk for<br>three-layer<br>HVH rout-<br>ing model<br>could be<br>devised | Firstly Algorithm<br>Net- Change after<br>that Track -<br>Interchange is con-<br>sider, so depend-<br>ence of algorithm<br>is there.                                       |

| "Channel<br>Based<br>Routing in<br>Channel-<br>less Cir-<br>cuits" Glau-<br>GlaucoBor-<br>coBor-<br>gesValim<br>dos Santos,<br>et al. [30]                                | 2006<br>IEEE                                                                                                                                  | JAVA<br>0.35µ<br>tech-<br>nology                | ChAOS ("chan-<br>nel assignment<br>toward full-<br>OTS synthesis")<br>router                                                                                                                                                                                                                                  | 0.6% increase in<br>wirelength<br>7.2% increase in<br>area                                                | Concen-<br>trate in<br>develop-<br>ing tools<br>that run<br>very fast<br>and can be<br>used in a<br>straight<br>forward<br>conver-<br>gent<br>methodol-<br>ogy for<br>layout<br>generation | No two<br>pins in<br>same row<br>can have<br>the same<br>x coordi-<br>nate | <ul> <li>a) three or<br/>more layer<br/>together<br/>with some<br/>optimiza-<br/>tion in data<br/>structures</li> <li>b) fast stei-<br/>ner tree<br/>heuristics<br/>be consid-<br/>ered at<br/>global<br/>planning<br/>for wire<br/>length re-<br/>duction</li> </ul> | Aligned Terminals<br>RoutingModel<br>(ATRM) in which<br>channel routing<br>algorithms can be<br>used to make con-<br>nections.                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "Via Mini-<br>mization<br>For Multi-<br>layer Chan-<br>nel Routing<br>in VLSI<br>Design"<br>Bhaskar<br>Das, Ashim<br>Kumar and<br>Ajoy Ku-<br>mar<br>Khan[31]             | 2014<br>IEEE<br>Fourth<br>Interna-<br>tional<br>Confer-<br>ence on<br>Commu-<br>nication<br>Systems<br>and Net-<br>work<br>Technolo-<br>gies. |                                                 | <ul> <li>a) Two layer<br/>channel:</li> <li>genetic algo-<br/>rithm</li> <li>with layout<br/>modification</li> <li>b)Three layer<br/>channel:</li> <li>with layout<br/>modification</li> <li>with layout<br/>modification</li> <li>with three lay-<br/>er channel rout-<br/>ing</li> <li>using BFS</li> </ul> | Reduction of<br>vias<br>Layout modifica-<br>tion : 34%<br>Using BFS :more<br>than 12% nd less<br>than 55% | Reduce<br>the num-<br>ber of vias<br>without<br>increasing<br>the rout-<br>ing area.                                                                                                       |                                                                            | Develop an<br>algorithm<br>for via<br>minimiza-<br>tion prob-<br>lem.                                                                                                                                                                                                 | <ul><li>a) Based on<br/>breadth first search</li><li>b) no specific rule<br/>for layering.</li></ul>                                                           |

| "Digital<br>Implemen-<br>tation of<br>16-bit Syn-<br>chronous<br>Counter<br>with SoC<br>Encounter<br>for Place-<br>ment and<br>Routing"<br>Pillem<br>Ramesh<br>and Venka- | 2012<br>Interna-<br>tional<br>Journal of<br>Engineer-<br>ing Re-<br>search and<br>Applica-<br>tion (IJE-<br>RA)                               | SoC<br>Encoun-<br>ter<br>130<br>tech-<br>nology | <ul> <li>a) floor planning</li> <li>b) power stripes</li> <li>c) placement</li> <li>d) generation of clock tree.</li> <li>e) detailed routing.</li> </ul>                                                                                                                                                     | Setup slack:<br>0.034ns<br>Hold slack :<br>0.016ns<br>Density :<br>90.079%                                | No DRC<br>violations.                                                                                                                                                                      |                                                                            |                                                                                                                                                                                                                                                                       | Helps physical<br>designer to assess<br>partition the logical<br>hierarchy and ana-<br>lyzing the optimal<br>pin assignments<br>time budgeting,<br>power grids |

| taAravindB<br>ezawa-<br>da[32]                                                                                                                                   |                                                                                              |                          |                                                                                                                                                                                                                                        |                                                                                                                                    |                                                                                                                                                                        |                                                                                                                         |                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| "Restorable<br>Routing<br>Algorithm<br>in optical<br>Networks<br>by Reduc-<br>ing Block-<br>ing Proba-<br>bil-<br>ity"Raman<br>Kumar and<br>Navneet-<br>Kaur[33] | 2014<br>IEEE<br>Proceed-<br>ings<br>RAECS<br>UIET<br>Punjab<br>University<br>Chandi-<br>garh |                          | Routing algo-<br>rithms:<br>a) WLCR-<br>FF(weighted<br>Least Congest-<br>ed Routing -<br>First fit)<br>b)shortest path<br>routing algo-<br>rithm<br>c)genetic algo-<br>rithm<br>d) Minimum<br>marginal cost<br>routing algo-<br>rithm. | Blocking probability :<br>-proposed algo-<br>rithm 8.6431×<br>10 <sup>-9</sup> %<br>Conventional<br>algorithm 4×10 <sup>-2</sup> % | Blocking<br>probabil-<br>ity of the<br>network<br>for pro-<br>posed<br>algorithm<br>increased<br>with the<br>increase in<br>the of-<br>fered load<br>per unit<br>link. | <br>                                                                                                                    | Number of light<br>paths is becoming<br>the main factor in<br>determining the<br>cost of WDM net-<br>work. |

| "A Hierar-<br>chical Ge-<br>netic Algo-<br>rithm for<br>Multi-<br>Layer<br>Channel<br>Routing"<br>Mark<br>P.Cloyed<br>and<br>Hesham H.<br>Ali[34]                | 2004<br>IEEE                                                                                 |                          | Hierarchical<br>Genetic Algo-<br>rithm.                                                                                                                                                                                                | Parameter was<br>incremented<br>from initial value<br>of 2 to a final<br>value 11.                                                 | Algorithm<br>utilized<br>the multi-<br>ple layers<br>to remove<br>vertical<br>con-<br>straints<br>and over-<br>come the<br>vertical<br>con-<br>strained<br>cycles.     |                                                                                                                         | This is the algo-<br>rithm which is ap-<br>plicable for multi-<br>layers.<br>( 2Lyr,<br>HVH,<br>VHV)       |

| "Chan-<br>nel/Switchb<br>ox Defini-<br>tion for<br>VLSI<br>Building-<br>Block Lay-<br>out" Yang<br>Cai and<br>D.F.Wong                                           | 1991<br>IEEE<br>Transac-<br>tions on<br>computer-<br>aided de-<br>sign.                      | Pascal<br>lan-<br>guage. | Comparison of :<br>Greedy algo-<br>rithm and<br>Minimum feed-<br>back vertex set<br>algorithm.                                                                                                                                         | No of Switch-<br>boxes is at most<br>2 more than the<br>optimal value                                                              | No of<br>switch-<br>boxes<br>generated<br>by our<br>algorithm<br>is only<br>about half<br>as greedy<br>algorithm                                                       | <br>Better algo-<br>rithms can<br>be devel-<br>oped to<br>minimize<br>the number<br>of L-<br>shaped<br>channels<br>used | Computation time<br>for large examples<br>are only a few se-<br>conds.                                     |

| [35]                                                                                                                                               |              |                                                                                                            |                                                      |                                                                                                                |                                                                                                                             |                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| "High Per-<br>formance<br>Multi-<br>Layer Rout-<br>ing for<br>VLSI Cir-<br>cuit Syn-<br>thesis"<br>Sangram-<br>jitBhowal ,<br>rajat K. Pal<br>[36] | 2004<br>IEEE | <br>MCCI Routing<br>solutions:<br>a) two layer VH<br>b)three-layer<br>VHV and HVH<br>c) four layer<br>VHVH | Crosstalk is re-<br>duced from 9<br>unit to 7 unit . | Minimize<br>routing<br>area and<br>reduce<br>total<br>crosstalk<br>in compu-<br>ting a<br>routing<br>solution. | <br>Reduce<br>total wire<br>length re-<br>quired in a<br>routing<br>solution<br>that may<br>optimize<br>signal de-<br>lays. | Amount of cross-<br>talk between wire<br>segments is propor-<br>tional to the cou-<br>pling capacitance. |

#### **IV. CONCLUSION**

In this paper a comparison on routing problems likeNP-hard andNP-complete based on different algorithms is done. We conclude that if the layers are increased than the number of tracks are reduced so that the NP-complete problem is solved and crosstalk is reduced. 50%, reduction in number of tracks, 30.77% reduced crosstalk[29]Gridless routing algorithm is much faster than grid routing algorithm(i.e around  $10\times$  speedup)[9]. These are the categories of manhattan channel routing. In channel-less circuits, channel based routing increase in wirelength and area.

#### REFERENCES

- [1] Ajoy Kumar Khan and Bhaskar Das, "A New Algorithm with Minimum Track for Four Layer Channel Routing in VLSI Design" *in proc. of IEEE International Conference on Computer Communication and Informatics*, Coimbatore, pp. 1-5, 2013.

- [2] Achira Pal, SwagataSahaSau, Tarak N. Mandal, Rajat K. Pal, Alak K. Datta, AtalChaudhuri, "Yet an Efficient Algorithm for Computing Reduced Are VLSI Channel Routing Solutions with Floating Terminals" in proc. of 14th International Confer ence on Computer and Information Technology, Bangladesh, pp.393-398, 22-24 Dec. 2011.

- [3] PralayMitra, NabinGhoshal, Rajit K. Pal, "A Graph Theoretic Approach to Minimize Total Wire Length in Channel Rout ing" *in proc. of IEEE Asic-Pacific Region*, pp. 414-418, 15-17 Oct. 2003.

- [4] SwagataSahaSau and Rajat Kumar Pal. "An Efficient High Performance Parallel Algorithm to Yield Reduced Wire Length VLSI Circuits" *in proc. of IEEE 5th International Conference on Computers and Devices for Communication(CODEC)*, pp.1-4, 17-19 Dec 2012.

- [5] M. NasirAyob, Fariz Hassan, A. Halim Ismail, H. Hassan Basri, M. SafwanAzmi, amarFaizZainal Abidin, "A Firefly Algo rithm Approach for Routing in VLSI" *in proc. of International Symposium on Computer Applications and Industrial Elec tronics (ISCAIE 2012)*, Malaysia, pp. 43-47, 3-4 Dec. 2012.

- [6] Yue Cao, Haitham Cruickshank and Zhili Sun, "A Rrouting Framework for Delay Tolerant Networks Based on En counter Angle" *in proc. of IEEE Wireless Communications and Mobile Computing conference(IWCMC),2011 7th International*, pp. 2231-2236, 2011.

- [7] Junbao Zhang, GuangchunLuo, Ke Qin, haifeng Sun, "Encounter-based routing in delay tolerant networks" *in proc. of Computational Problem-Solving*)(*ICCP*), pp. 338-341, 2011.

- [8] Yanheng Zhang and Chris Chu, "GDRouter: Interleaved Global Routing and Detailed Routing for Ultimate Routability" *in proc. of Design Automation Conference(DAC)*, pp. 597-602, 2012.

- [9] QiangGao, Hailong Yao, Qiang Zhou, YiciCai, "A Novel Detailed Routing Algorithm with Exact Matching Constraint for Analog and Mixed Signal Circuits" *in proc. of IEEE 12th Int'l Symposium on Quality Electronic Design*, pp. 36-41, 2011.

- [10] Yi-Huang Hung, Hung-Yi Li, Hung-Yi Li, Yi-Yu Liu, "Dangling-wire Avoidance Routing for Crossbar Switch Structured ASIC Design Style" *in proc. VLSI Design Automation and Test (VLSI-DAT), 2010 International Symposium* of IEEE, pp.177-180, 2010.

- [11] Shyamapada Mukherjee and Suchismita Roy, "Graph Colouring Based Multi Pin Net Detailed Routing For FPGA using SAT" *in proc. of 3rd IEEE International Advance Computing Conference (IACC)*, pp. 308-312, 2012.

- [12] XuZhenghua, "The Automation design Based on Graphs for the Symmetrical Routing in Integrated Circuit" *in proc. of IEEE International Conference on System Science, Engineering Design and Manufacturing Informatization*, pp. 331-334, 2011.

- [13] Christopher CondratPriyankKalla, Steve Blair, "Crossing-aware channel routing for photonic waveguides" in proc. of Circuits and Systems (MWSCAS), 2013 IEEE 56th International Midwest Symposium\_, pp. 649-652, 2013.

- [14] Shuai Li and Cheng-KokKoh, "Analytical Placement of Mixed-size Circuits for Better Detailed- Routability" *in proc. of IEEEDesign Automation Conference (ASP-DAC)*, pp. 41-46, 2014.